# PCIe Endpoint Controller SB16C1154PCIe

**Revision 1.0 Preliminary**

SystemBase Co., Ltd.

# SB16C1154PCle

PCIe End Point Controller with Quad-UART

April 2014 REV 1.0 Preliminary

# CONTENTS

| 1. Description                                              |

|-------------------------------------------------------------|

| 2. Features                                                 |

| 2.1 PCI Express Interface                                   |

| 2.2 Serial Interface                                        |

| 2.3 Miscellaneous                                           |

| 2.4 Development Kit → Manufacturing Kit ??                  |

| 3. Ordering Information                                     |

| 4. Block Diagram                                            |

| 5. Applications                                             |

| 5.1 Serial 4-port                                           |

| 6. Pin Configuration                                        |

| 6.1 Pin Configuration for 176-Pin TQFP Package10            |

| 6.2 Pin Description                                         |

| 7. Configuration Loader                                     |

| 7.1 Serial EEPROM Information Table15                       |

| 8. PCIe Configuration Space                                 |

| 8.1 Configuration Registers                                 |

| 8.1.1 Configuration Register Types                          |

| 8.1.2 Configuration Space Map of SB16C1154PCIe              |

| 8.2 PCI Compatible Configuration Registers of SB16C1154PCIe |

| 8.2.1 Vendor ID                                             |

| 8.2.2 Device ID                                             |

| 8.2.3 Command Register                                      |

| 8.2.4 Status Register                                       |

| 8.2.5 Revision                                              |

| 8.2.6 Class Code                                            |

| 8.2.7 Cache Line Size                                       |

| 8.2.8 Latency Timer                                         |

| 8.2.9 Header Type23                                         |

| 8.2.10 BIST(Built-In Self Test)                             |

| 8.2.11 Base Address Registers                               |

| 8.3 Power Management Registers of SB16C1154PCIe24           |

# SB16C1154PCIe PCIe Endpoint Controller with Quad-UART April 2014 REV 1.0 Preliminary

| 8.3.1 Capability ID (offset: 0x0)                                                | 24 |

|----------------------------------------------------------------------------------|----|

| 8.3.2 Pointer to Next Capability (offset: 0x01)                                  | 24 |

| 8.3.3 Power Management Capabilities (offset: 0x02)                               | 25 |

| 8.3.4 Power Management Control/Status Register (offset: 0x04)                    | 25 |

| 8.3.5 PMCSR PCI-to-PCI Bridge Support Extensions (offset: 0x06)                  | 26 |

| 8.3.6 Power Management Data Register (offset: 0x07)                              | 26 |

| 8.4 Message Signaled Interrupt Registers of SB16C1154PCIe                        | 26 |

| 8.4.1 Capability ID (offset: 0x0)                                                | 27 |

| 8.4.2 Pointer to Next Capability (offset: 0x01)                                  | 27 |

| 8.4.3 Message Control Register (offset: 0x02)                                    | 27 |

| 8.4.4 MSI Data Register (offset: 0x08; if MSI 64 EN is 1b, offset: 0x0C)         | 27 |

| 8.4.5 MSI Mask Bits Register (offset: 0x0C; if MSI 64 EN is 1b, offset: 0x10)    | 27 |

| 8.4.6 MSI Pending Bits Register (offset: 0x10; if MSI 64 EN is 1b, offset: 0x14) | 28 |

| 8.5 PCI Express Specific Configuration Registers of SB16C1154PCIe                | 28 |

| 8.5.1 Capability ID (offset: 0x0)                                                | 28 |

| 8.5.2 Pointer to Next Capability (offset: 0x01)                                  | 28 |

| 8.5.3 PCI Express Capabilities Register (offset: 0x02)                           | 28 |

| 8.5.4 PCI Express Device Capabilities Register (offset: 0x04)                    | 29 |

| 8.5.5 Device Control Register (offset: 0x08)                                     | 30 |

| 8.5.6 Device Status Register (offset: 0x0A)                                      | 31 |

| 8.5.7 Link Capabilities Register (offset: 0x0C)                                  | 31 |

| 8.5.8 Link Control Register (offset: 0x10)                                       | 32 |

| 8.5.9 Link Status Register (offset: 0x12)                                        | 33 |

| 8.5.10 Device Capabilities 2 Register (offset: 0x24)                             | 33 |

| 8.5.11 Device Control 2 Register (offset: 0x28)                                  | 34 |

| 8.5.12 Link Capabilities 2 Register (offset: 0x2C)                               | 34 |

| 8.5.13 Link Control 2 Register (offset: 0x30)                                    | 35 |

| 8.5.14 Link Status 2 Register (offset: 0x32)                                     | 35 |

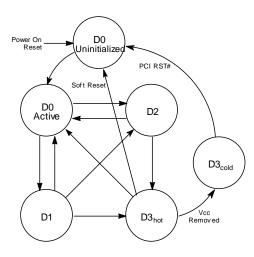

| 9. Power Management                                                              | 36 |

| 9.1 PCI Express Power Management                                                 | 36 |

| 9.1.1 PCIe Function Power State                                                  | 36 |

| 9.1.2 Sticky Bits (PME Context)                                                  | 37 |

| 9.1.3 Wakeup Protocol                                                            | 37 |

| 9.1.4 PME Service                                                                | 38 |

| 9.1.5 PME Service Timeout Protocol                                               | 39 |

| 9.2 SB16C1154PCIe Power Management Pins and Functions                            | 39 |

April 2014 REV 1.0 Preliminary

| 9.2.1 SB16C1154PCIe Pins for Power Management               |

|-------------------------------------------------------------|

| 9.2.2 SB16C1154PCIe Power Management Wakeup implementation  |

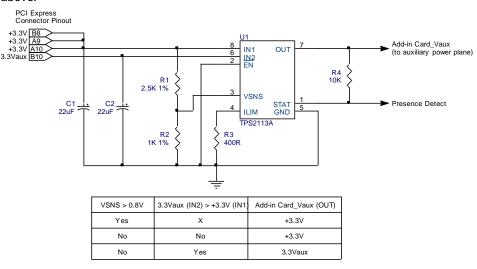

| 9.2.3 VIO_AUX Presence Detection & Power Routing            |

| 10. UART Space                                              |

| 10.1 UART I/O Address Map                                   |

| 11. Option I/O Space                                        |

| 11.1 General Information Register0 – Port Number (GIR0)     |

| 11.2 General Information Register1 – Product Version (GIR1) |

| 11.3 General Information Register2 – Operation Mode (GIR2)  |

| 11.4 General Information Register3 – Core Version (GIR3)    |

| 11.5 Software Reset Register                                |

| 11.6 Device Information Register0 ~ 3 (DIR0 ~ 3)            |

| 11.7 Interface Information Register0 ~ 3 (IIR0 ~ 3)         |

| 11.8 Interrupt Mask Register0 ~ 3 (IMR0 ~ 3)                |

| 11.9 Interrupt Poll Register0 ~ 3 (IPR0 ~ 3)                |

| 11.10 Auto Toggle Pin Select Register (ATPSR)               |

| 11.11 PM_PME Message Resource Register (PPMRR)              |

| 11.12 General Purpose Outputs Control Register (GPOCR)      |

| 11.13 General Purpose Outputs Data Register (GPODR)         |

| 11.14 General Purpose Inputs Data Register (GPIDR)          |

| 11.12 General Purpose Outputs Control Register 2 (GPOCR2)   |

| 11.13 General Purpose Outputs Data Register 2 (GPODR2)      |

| 11.14 General Purpose Inputs Data Register 2 (GPIDR2)       |

| 12. UART(SB16C1150) Functional Description                  |

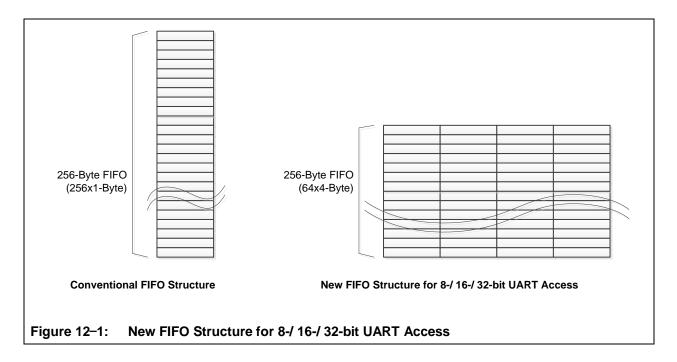

| 12.1 FIFO Operation                                         |

| 12.2 Hardware Flow Control                                  |

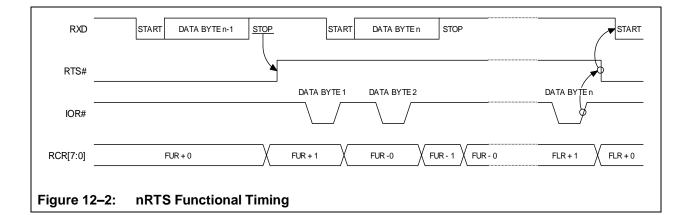

| 12.2.1 Auto-RTS                                             |

| 12.2.2 Auto-CTS                                             |

| 12.3 Software Flow Control                                  |

| 12.3.1 Transmit Software Flow Control53                     |

| 12.3.2 Receive Software Flow Control                        |

| 12.3.3 Xon Any Function                                     |

| 12.3.4 Xoff Re-transmit Function                            |

| 12.4 Sleep Mode with Auto Wake-Up57                         |

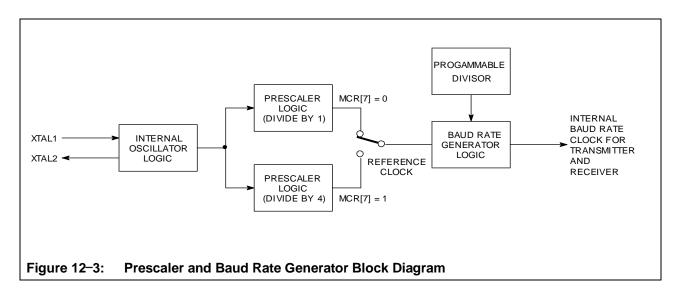

| 12.5 Programmable Baud Rate Generator ← 29.4912MHz clock in |

# SB16C1154PCle PCIe Endpoint Controller with Quad-UART April 2014 REV 1.0 Preliminary

**REV 1.0 Preliminary**

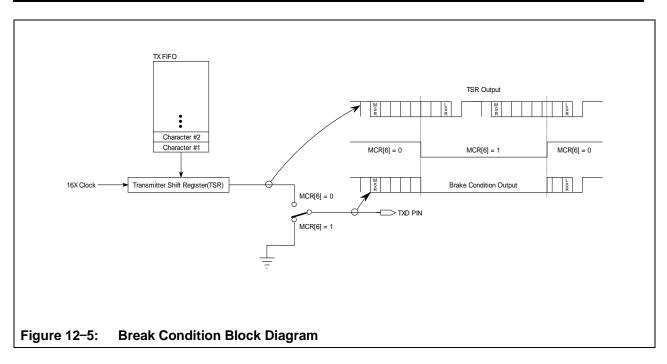

| 12.6 Break and Time-out Conditions                                              | 59   |

|---------------------------------------------------------------------------------|------|

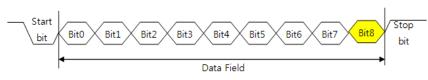

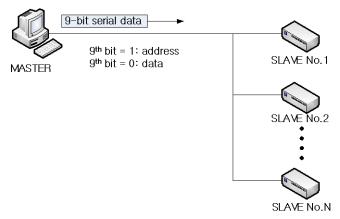

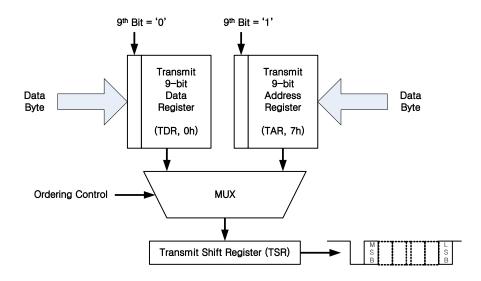

| 12.7 Multi Drop Mode (9-bit Data Transmission)                                  | 61   |

| 12.7.1 Transmit 9-bit Address Register (TAR) / Transmit 9-bit Data Register(TDI | R)62 |

| 12.7.2 Automatic Address Compare                                                | 64   |

| 12.7.3 Changed Register Map                                                     | 65   |

| 13. UART(SB16C1150) Register Descriptions                                       | 67   |

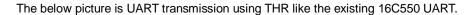

| 13.1 Transmit Holding Register (THR, 00h, Output Port)                          | 71   |

| 13.2 Transmit 9-bit Data Byte Register (TDR, 00h, Output Port)                  | 71   |

| 13.3 Receive Buffer Register (RBR, 00h, Input Port)                             | 71   |

| 13.4 Interrupt Enable Register (IER, 01h, Input/Output Port)                    | 71   |

| 13.5 Interrupt Status Register (ISR, 02h, Input Port)                           | 72   |

| 13.6 FIFO Control Register (FCR, 02h, Output Port)                              | 74   |

| 13.7 Line Control Register (LCR, 03h, Input/Output Port)                        | 74   |

| 13.8 Modem Control Register (MCR, 04h, Input/Output Port)                       | 75   |

| 13.9 Line Status Register (LSR, 05h, Input Port)                                | 76   |

| 13.10 Software Toggle Register (STR, 05h, Output Port)                          | 77   |

| 13.11 Modem Status Register (MSR, 06h, Input Port)                              | 78   |

| 13.12 Multi Drop mode Register (MDR, 06h, Output Port)                          | 78   |

| 13.13 Scratch Pad Register (SPR, 07h, Input/Output Port)                        | 79   |

| 13.14 Transmit 9-bit Address Register (TAR, 07h, Output Port)                   | 79   |

| 13.15 Divisor Latches (DLL/DLM, 08h/09h, Input/Output Port)                     | 80   |

| 13.16 Enhanced Features Register (EFR, 0Ah, Input/Output Port)                  | 80   |

| 13.17 Clock Prescaler Register (CPR, 0Bh, Input/Output)                         | 81   |

| 13.18 Receiver Mode Selection Register (RMR, 0Ch, Input/Output Port)            | 81   |

| 13.19 Auto Toggle Register (ATR, 0Dh, Input/Output Port)                        | 82   |

|                                                                                 |      |

00

April 2014 REV 1.0 Preliminary

| 13.25 Flow Control Lower Threshold Register (FLR, 13h, Input/Output)                    |

|-----------------------------------------------------------------------------------------|

| 13.26 Transmitter FIFO Count Register LSB (TCRL, 14h, Input)                            |

| 13.27 Transmitter FIFO Count Register MSB (TCRH, 15h, Input)                            |

| 13.28 Receiver FIFO Count Register LSB (RCRL, 16h, Input)                               |

| 13.29 Receiver FIFO Count Register MSB (RCRH, 17h, Input)                               |

| 13.30 Xon1 Character Register (XON1, 14h, Output)87                                     |

| 13.31 Xon2 Character Register (XON2, 15h, Output)87                                     |

| 13.32 Xoff1 Character Register (XOFF1, 16h, Output)87                                   |

| 13.33 Xoff2 Character Register (XOFF2, 17h, Output)                                     |

| 13.34 Receive FIFO Register 0 (RX0, 18h, Input)                                         |

| 13.35 Receive FIFO Register 1 / Receive Line Status Register 0 (RX1/RXS0, 19h, Input)87 |

| 13.36 Receive FIFO Register 2 / Receive FIFO Register 1 (RX2/RX1, 1Ah, Input)87         |

| 13.37 Receive FIFO Register 3 / Receive Line Status Register 0 (RX3/RXS1, 1Bh, Input)87 |

| 13.38 Transmit FIFO Register 0 (TX0, 1Ch, Output)88                                     |

| 13.39 Transmit FIFO Register 1 (TX1, 1Dh, Output)88                                     |

| 13.40 Transmit FIFO Register 2 (TX2, 1Eh, Output)                                       |

| 13.41 Transmit FIFO Register 3 (TX3, 1Fh, Output)89                                     |

| 14. Electrical Information ← 내용 아이칩스에서 받아서 적용 예정90                                      |

| 14.1 Absolute Maximum Ratings90                                                         |

| 14.2 Recommended Operating Conditions90                                                 |

| 14.3 DC Characteristics of I/O90                                                        |

| 14.4 I/O Classification                                                                 |

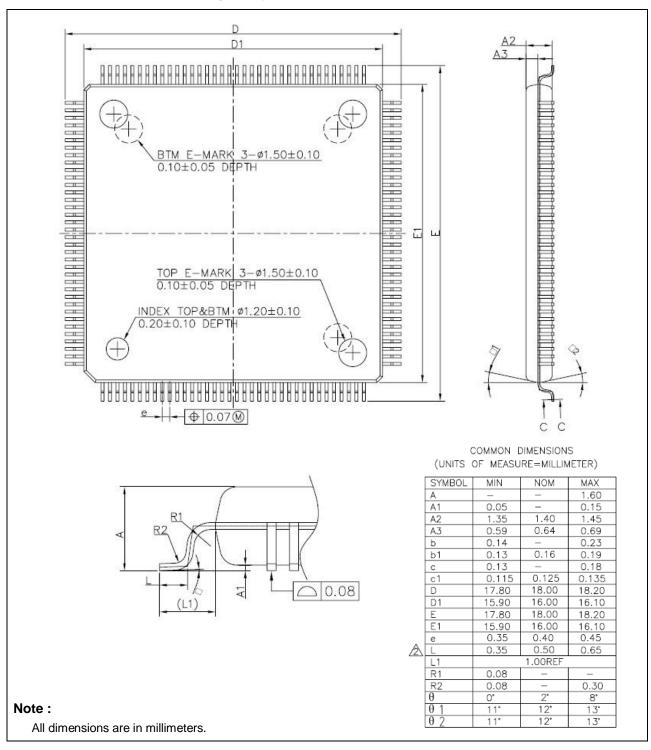

| 15. Package Outline                                                                     |

# SB16C1154PCIe

PCIe End Point Controller with Quad-UART

April 2014 REV 1.0 Preliminary

#### 1. Description

SB16C1154PCIe is a PCI Express Endpoint Controller with Quad-UART Interface. It offers easy PCI Express Endpoint Card Adapter implementation with a built-in PCIe PHY. SB16C1154PCIe provides high performance serial communication. With a built-in four SB16C1150 Cores that has 256-byte FIFO, SB16C1154PCIe decreases CPU load, is stronger at errors such as Overrun error and works well with simultaneous use of multiple ports. Because SB16C1154PCIe support PCI Express Burst Transfer up to 256-byte and it have built-in four enhanced 8-bit/ 16-bit/ 32-bit accessible UART core. Furthermore, it is capable of waking up PC that is powered off through external Wake-up Requests with PCI Express Power Management implemented. SB16C1154PCIe provides RS422/485 Auto Toggling function and Global Interrupt Function to the built-in UART allowing a more convenient handling of serial communication at a driver level. Finally, with SB16C1154PCIe, it is easy to design and fix the serial cards because it have TQFP 144 package.

#### 2. Features

#### 2.1 PCI Express Interface

- Compliant with PCI Express Base Specification, Revision 1.0a , 1.1 and 2.0

- PCI Express Single-Lane(x1), Compatible with x4, x8 and x16 PCI Express slots

- Built-In x1 PCI Express PHY

- Up to 256-byte PCI Express Burst Operation for serial dump

- One Virtual Channel

- INTx emulation & Message Signaled Interrupt(MSI)

- PCI Express Power Management,

Supports PCI-PM Rev 1.2 - D0, D3hot and D3cold

- Supports ASPM L0s, L1

- Download PCI Express Configuration Data from external serial EEPROM

#### 2.2 Serial Interface

- Built-In four Enhanced UART Core, 16C1150 with 256-byte Tx/Rx FIFO

- Up to 3.9 Mbps Baud Rate (Up to 62.5 MHz Oscillator Input Clock)

- 256-byte Transmit FIFO

- 256-byte Receive FIFO with Error Flags

- Support 9-bit Serial Communication and Auto Address Detection

- Support Enhanced Auto Toggling

- 32-bit/ 16-bit/ 8-bit Accessible UART Core

- Support IrDA v1.0/v1.1 Encoding/Decoding

- Programmable and Selectable Transmit and Receive FIFO Trigger Levels for Interrupt Generation

- Software (Xon/Xoff) / Hardware (nRTS/nCTS) Flow Control

- Programmable Xon/Xoff Characters

- Programmable Auto-RTS and Auto-CTS

April 2014 REV 1.0 Preliminary

- Interrupt Poll Control

- Optional Data Flow Resume by Xon Any Character Control

- Optional Data Flow Additional Halt by Xoff Re-transmit Control

- Control pins for RS-422 Point to Point/Multi-Drop Auto Control

- Control pins for RS-485 Echo/Non Echo Auto Control

- Software Selectable Baud Rate Generator

- Prescaler Provides Additional Divide-by-4 Function

- Fast Data Bus Access Time

- Programmable Sleep Mode

- Programmable Serial Interface Characteristics

- 5, 6, 7, or 8-bit Characters

- Even, Odd, or No Parity Bit Generation and Detection

- 1, 1.5, or 2 Stop Bit Generation

- False Start Bit Detection

- Line Break Generation and Detection

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (nRTS, nCTS, nDTR, nDSR, nDCD, and nRI)

#### 2.3 Miscellaneous

- 1.2V and 3.3V Operation

- 5V Tolerant Inputs

- Support 16 GPIO channels

- Industrial Temperature Operating, -40°C ~ +85°C

- TQFP144 package

- Application

- 4-port serial multiport PCIe card

#### 2.4 Development Kit → Manufacturing Kit ??

SystemBase offers the SB16C1154PCIe Development Kit to minimize efforts and costs, and to maximize application stability.

SB16C1154PCIe Development Kit includes Hardware schematics, PCB CAD files, software device driver and source codes and etc.

It will help you develop a new product easily and quickly.

#### 3. Ordering Information

#### Table 3–1: Ordering Information

| Part Number      | Package      | Operating Temperature Range | Device Status |

|------------------|--------------|-----------------------------|---------------|

| SB16C1154PCIe-TQ | 144-Pin TQFP | -40 °C to +85 °C            | Active        |

April 2014 REV 1.0 Preliminary

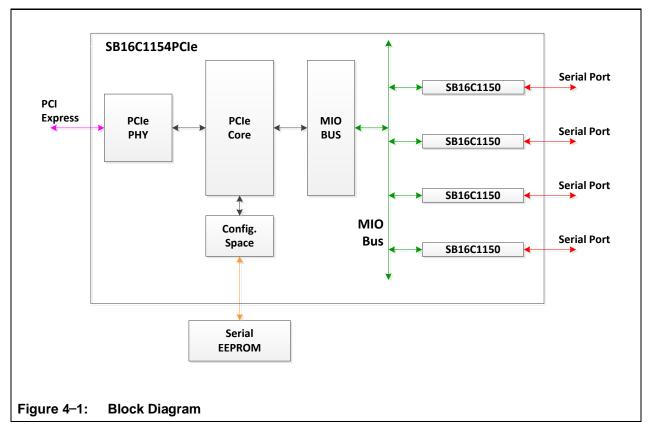

#### 4. Block Diagram

### SB16C1154PCle PCIe Endpoint Controller with Quad-UART April 2014 REV 1.0 Preliminary

#### 5. Applications

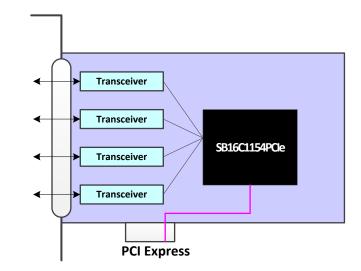

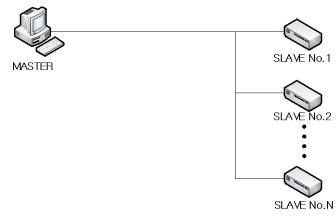

5.1 Serial 4-port

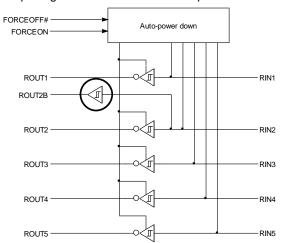

Figure 5–1: Serial 4-port Mode Application Block Diagram

4-port Serial card is generally made with SB16C1154PCIe (called by Serial 4-port Mode). Special logic is not needed to make 4-port serial Multi-Port since Quad-UART is built inside the SB16C1154PCIe. Depending on Serial Interface, Transceiver IC of the RS232, RS422 or RS485 needs to be attached for long distance transmission.

April 2014 REV 1.0 Preliminary

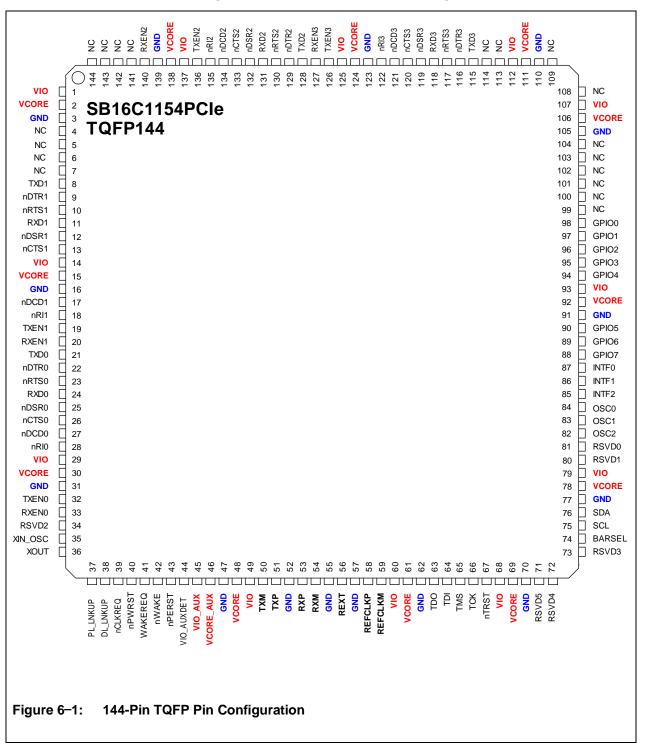

#### 6. Pin Configuration

#### 6.1 Pin Configuration for 144-Pin TQFP Package

# SB16C1154PCle PCIe Endpoint Controller with Quad-UART April 2014 REV 1.0 Preliminary

#### 6.2 Pin Description

#### Table 6–1: Pin Description

| PCI Express Bus Interface |     |      |                                                                                        |

|---------------------------|-----|------|----------------------------------------------------------------------------------------|

| Name                      | Pin | Туре | Description                                                                            |

| TXP                       | 51  | 0    | PCI Express Transmitter Differential Pair: PCI Express differential pair               |

| TXM                       | 50  | 0    | output from PHY. All the transmitter should be AC-coupled to media.                    |

| RXP                       | 53  | I.   | PCI Express Receiver Differential Pair: PCI Express differential pair input            |

| RXM                       | 54  | I    | to PHY with 50ohm on-chip termination.                                                 |

| REFCLKP                   | 58  | I    | 100MHz Reference Clock: This is the spread spectrum source clock for                   |

| REFCLKM                   | 59  | I    | PCI Express. Differential pair input with 50ohm on-chip termination and                |

|                           |     |      | nominal frequency of 100MHz±300PPM.                                                    |

| nPERST                    | 43  | I    | PCI Express Fundamental Reset: Reset the SB16C1154PCIe. The                            |

|                           |     |      | inputted signal indicates when the applied main power is within the specified          |

|                           |     |      | tolerance and stable. This signal is asynchronous.                                     |

| nWAKE                     | 42  | 0    | Signal for Link Reactivation: The open-drain output, active low signal that            |

|                           |     |      | is driven to reactivate the PCI Express Link hierarchy's main power rails and          |

|                           |     |      | reference clocks.                                                                      |

| REXT                      | 56  | 0    | <b>Register for the reference current :</b> Connects $190\Omega$ 1% resistor with GND. |

| WAKEREQ                   | 41  | I.   | WAKE Request: LTSSM of PCI Express Device goes from L2 state to L0                     |

|                           |     |      | state with the Wake Up Event. This pin receives the event signal needed for            |

|                           |     |      | the transition from L2 state to L0 state.                                              |

| nCLKREQ                   | 39  | 0    | PCI Express Connector Clock Request: Clock Request Signal                              |

| PL_LNKUP                  | 37  | 0    | Physical Layer Linkup Indicator: This pin is used to indicate whether PCI              |

|                           |     |      | Express physical layer linked up or not.                                               |

| DL_CLKUP                  | 38  | 0    | Data Link Layer Linkup Indicator: This pin is used to indicate whether PCI             |

|                           |     |      | Express physical layer linked up or not.                                               |

| VIO_AUXDET                | 44  | I    | Detection for Auxiliary VIO power: Detect Auxiliary VIO power                          |

| Modem and Serial I/O Interface |     |        |                                                                              |  |

|--------------------------------|-----|--------|------------------------------------------------------------------------------|--|

| Name                           | Pin | Туре   | Description                                                                  |  |

| TXD0                           | 21  | 0      | Transmit Data: These pins are individual transmit data output. During the    |  |

| TXD1                           | 8   | 0      | local loop-back mode, the TXD output pin is disabled and TXD data is         |  |

| TXD2                           | 128 | 0      | internally connected to the RXD input.                                       |  |

| TXD3                           | 115 | 0      |                                                                              |  |

| RXD0                           | 24  | I (PU) | Receive Data: These pins are individual receive data input. During the local |  |

| RXD1                           | 11  | I (PU) | loop-back mode, the RXD input pin is disabled and RXD data is internally     |  |

| RXD2                           | 131 | I (PU) | connected to the TXD output.                                                 |  |

| RXD3                           | 118 | I (PU) |                                                                              |  |

| nRTS0                          | 23  | 0      | Request to Send (active low): These pins indicate that the UART is ready     |  |

| nRTS1                          | 10  | 0      | to receive data from the modem, and affect transmit and receive operations   |  |

| nRTS2                          | 130 | 0      | only when Auto-RTS function is enabled.                                      |  |

| nRTS3                          | 117 | 0      |                                                                              |  |

April 2014 REV 1.0 Preliminary

| Modem and Serial I/O Interface |     |        |                                                                                  |

|--------------------------------|-----|--------|----------------------------------------------------------------------------------|

| Name                           | Pin | Туре   | Description                                                                      |

| nCTS0                          | 26  | I (PU) | Clear to Send (active low): These pins indicate the modem is ready to            |

| nCTS1                          | 13  | I (PU) | receive transmitted data from the UART, and affect transmit and receive          |

| nCTS2                          | 133 | I (PU) | operations only when Auto-CTS function is enabled.                               |

| nCTS3                          | 120 | I (PU) |                                                                                  |

| nDTR0                          | 22  | 0      | Data Terminal Ready (active low): These pins indicate UART is ready for          |

| nDTR1                          | 9   | 0      | data exchange with modem after self initialization.                              |

| nDTR2                          | 129 | 0      |                                                                                  |

| nDTR3                          | 116 | 0      |                                                                                  |

| nDSR0                          | 25  | I (PU) | Data Set Ready (active low): These pins indicate modem is powered-on             |

| nDSR1                          | 12  | I (PU) | and is ready for data exchange with UART.                                        |

| nDSR2                          | 132 | I (PU) |                                                                                  |

| nDSR3                          | 119 | I (PU) |                                                                                  |

| nDCD0                          | 27  | I (PU) | Carrier Detect (active low): These pins indicate that a carrier has been         |

| nDCD1                          | 17  | I (PU) | detected by modem.                                                               |

| nDCD2                          | 134 | I (PU) |                                                                                  |

| nDCD3                          | 121 | I (PU) |                                                                                  |

| nRI0                           | 28  | I (PU) | Ring Indicator (active low): These pins indicate the modem has received a        |

| nRI1                           | 18  | I (PU) | ringing signal from telephone line. A low to high transition on these input pins |

| nRI2                           | 135 | I (PU) | generates a modem status interrupt, if enabled.                                  |

| nRI3                           | 122 | I (PU) |                                                                                  |

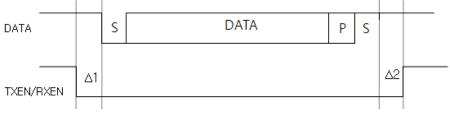

| TXEN0                          | 32  | 0      | <b>TX Enable:</b> This pin is for Auto tri-state control of the RS422 or RS485   |

| TXEN1                          | 19  | 0      | communication (Auto Toggling). When serial date is transmitted to TXD, the       |

| TXEN2                          | 136 | 0      | value set on ATR[5] is transmitted.                                              |

| TXEN3                          | 126 | 0      | These pins eliminate additional glue logic outside.                              |

| RXEN0                          | 33  | 0      | <b>RX Enable:</b> This pin is for Auto tri-state control of the RS422 or RS485   |

| RXEN1                          | 20  | 0      | communication (Auto Toggling). When serial date is transmitted to TXD, the       |

| RXEN2                          | 140 | 0      | value set on ATR[7] is transmitted.                                              |

| RXEN3                          | 127 | 0      | These pins eliminate additional glue logic outside.                              |

#### Table 6–1: Pin Description...continued

| Function Configuration Interfaces |     |      |                                                                             |

|-----------------------------------|-----|------|-----------------------------------------------------------------------------|

| Name                              | Pin | Туре | Description                                                                 |

| INTF0                             | 87  | I    | Line Interface Type Select: These pins are used to select the type of Line  |

| INTF1                             | 86  | I    | Transceiver interfaced in Serial 4-port Mode. The inputted value from these |

| INTF2                             | 85  | I    | pins is shown in IIR0[6:4] of the Option register.                          |

|                                   |     |      | INTF[2:0] = 0xxb : RS232 transceiver is selected.                           |

|                                   |     |      | INTF[2:0] = 100b : RS422 transceiver with 1:1 mode is selected.             |

|                                   |     |      | INTF[2:0] = 101b : RS422 transceiver with Multi-Drop mode is selected.      |

|                                   |     |      | INTF[2:0] = 110b : RS485 transceiver with Non-Echo mode is selected.        |

|                                   |     |      | INTF[2:0] = 111b : RS485 transceiver with Echo mode is selected.            |

SB16C1154PCIe

PCIe Endpoint Controller with Quad-UART April 2014 REV 1.0 Preliminary

| Function Configuration Interfaces |     |      |                                                                          |

|-----------------------------------|-----|------|--------------------------------------------------------------------------|

| Name                              | Pin | Туре | Description                                                              |

| OSC0                              | 84  | I    | Oscillator Select: These pins are used to select the type of Oscillator. |

| OSC1                              | 83  | I    | The inputted value from these pins are shown in DIR0[3:0] of the Option  |

| OSC2                              | 82  | I    | register.                                                                |

|                                   |     |      | OSC[2:0] = 000b : 1.8432MHz (up to 115.2Kbps)                            |

|                                   |     |      | OSC[2:0] = 001b : 3.6864MHz (up to 230.4Kbps)                            |

|                                   |     |      | OSC[2:0] = 010b : 7.3728MHz (up to 460.8Kbps)                            |

|                                   |     |      | OSC[2:0] = 011b : 14.7456MHz (up to 921.6Kbps)                           |

|                                   |     |      | OSC[2:0] = 100b : 29.4912MHz (up to 1.8432Mbps)                          |

| BARSEL                            | 74  | I    | Base Address Range Select:                                               |

|                                   |     |      | When this pin is 0b, it allocates Base Address Ranges as a I/O space. So |

|                                   |     |      | you can set the serial card to I/O mapped I/O.                           |

|                                   |     |      | When this pin is 1b, it allocates Base Address Ranges as a Memory space. |

|                                   |     |      | You can set the serial card to Memory mapped I/O (default)               |

| Serial EEPROM Interfaces |     |      |                                                                     |

|--------------------------|-----|------|---------------------------------------------------------------------|

| Name                     | Pin | Туре | Description                                                         |

| SDA                      | 76  | I/O  | Serial EEPROM Data Input/Output: Connected to SDA of serial EEPROM. |

| SCL                      | 75  | 0    | Serial EEPROM Clock Output: Connected to SCL of serial EEPROM.      |

| GPIO Interfaces |     |      |                                                                    |

|-----------------|-----|------|--------------------------------------------------------------------|

| Name            | Pin | Туре | Description                                                        |

| GPIO0           | 98  | I/O  | General Purpose Input and Output: The directions of these pins are |

| GPIO1           | 97  |      | controlled by GPOCR of the Option Register.                        |

| GPIO2           | 96  |      | Inputted data is stored in GPIDR of the Option Register.           |

| GPIO3           | 95  |      | Output data is determined by GPODR of the Option Register.         |

| GPIO4           | 94  |      |                                                                    |

| GPIO5           | 90  |      |                                                                    |

| GPIO6           | 89  |      |                                                                    |

| GPIO7           | 88  |      |                                                                    |

| Other Interfaces |     |      |                                                                                                                                                                                                                               |

|------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name             | Pin | Туре | Description                                                                                                                                                                                                                   |

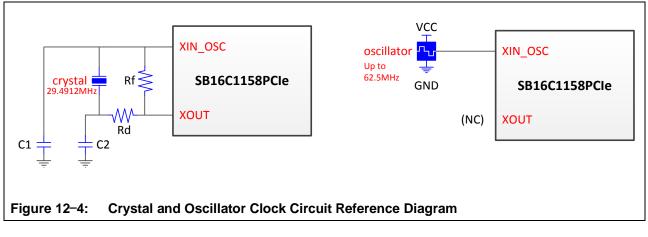

| XIN_OSC          | 35  | I    | <b>Crystal or External Clock Input:</b> This input of up to 62.5MHz for data rate of 3.9Mbps at 1.2V. When OSC_SEL=1, SB16C1154PCIe use crystal as clock source. In this case, OSC_IN is not used and have to be wired to 0b. |

| XOUT             | 36  | 0    | Crystal or Buffed Clock Output: This is output from resonant circuit of crystal.                                                                                                                                              |

| nPWRST           | 40  | I    | Power On Resets                                                                                                                                                                                                               |

April 2014 REV 1.0 Preliminary

| Reserved Pins for TEST |     |      |                                                            |  |

|------------------------|-----|------|------------------------------------------------------------|--|

| Name                   | Pin | Туре | Description                                                |  |

| RSVD0                  | 81  | I    | Reserved inputs for test.                                  |  |

| RSVD1                  | 80  | I    | Please make these reserved pins pull-down.                 |  |

| RSVD2                  | 34  | Ι    |                                                            |  |

| RSVD3                  | 73  | I    | Reserved inputs for test mode selection.                   |  |

| RSVD4                  | 72  | I    | Please make these reserved pins pull-up with 10K resistor. |  |

| RSVD5                  | 71  | I    |                                                            |  |

| TDO                    | 63  | 0    | JTAG Interfaces for TEST.                                  |  |

| TDI                    | 64  | I    | Please make output pins open.                              |  |

| TMS                    | 65  | I    | Please make input pins pull-up.                            |  |

| TCK                    | 66  | I    |                                                            |  |

| nTRST                  | 67  | 0    |                                                            |  |

| Power and Ground |                      |      |                                                              |  |  |

|------------------|----------------------|------|--------------------------------------------------------------|--|--|

| Name             | Pin                  | Туре | Description                                                  |  |  |

| VIO              | 1, 14, 29, 49, 60,   | PWR  | Power Supply for Digital I/O: Connect to +3.3V and to I/O    |  |  |

|                  | 68, 79, 93, 107,     |      | Ground through 0.1uF capacitors.                             |  |  |

|                  | 112, 125, 137        |      |                                                              |  |  |

| VCORE            | 2, 15, 30, 48, 61,   | PWR  | Power Supply for Digital Core: Connect to +1.2V and to Core  |  |  |

|                  | 69, 78, 92, 106,     |      | Ground through 0.1uF capacitors.                             |  |  |

|                  | 111, 124, 138        |      |                                                              |  |  |

| VIO_AUX          | 45                   | PWR  | Auxiliary Power Supply for Digital I/O: Connect to +3.3V_aux |  |  |

|                  |                      |      | and to I/O Ground through 0.1uF capacitors.                  |  |  |

| VCORE_AUX        | 46                   | PWR  | Auxiliary Power Supply for Digital Core: Connect to          |  |  |

|                  |                      |      | +1.2V_aux and to Core Ground through 0.1uF capacitors.       |  |  |

| GND              | 3, 16, 31, 47, 52,   | GND  | Ground for Digital Core: Connect to ground.                  |  |  |

|                  | 55, 57, 62, 70, 77,  |      |                                                              |  |  |

|                  | 91, 105, 110, 123,   |      |                                                              |  |  |

|                  | 139                  |      |                                                              |  |  |

| NC               | 4, 5, 6, 7, 99, 100, | -    | No Connect:                                                  |  |  |

|                  | 101, 102, 103, 104,  |      |                                                              |  |  |

|                  | 108, 109, 113, 114,  |      |                                                              |  |  |

|                  | 141, 142, 143, 144   |      |                                                              |  |  |

SB16C1154PCle

PCIe Endpoint Controller with Quad-UART

April 2014 REV 1.0 Preliminary

#### 7. Configuration Loader

SB16C1154PCIe can perform system initialization by reading PCI Express Configuration header data from Internal MIO registers or external serial EEPROM. It is decided to download configuration header data through exist of external serial ROM. SB16C1154PCIe use a 256K I<sup>2</sup>C serial EEPROM (24C256). We recommend customers use ATMEL AT24C256 or CATALYST CA24C256 for external serial ROM. When SB16C1154PCIe is reset after power is granted, Configuration Loader inside SB16C1154PCIe loads Configuration header data and etc from internal MIO registers or external serial EEPROM depending on the existence of external EXT\_LOAD pin. If external serial ROM exist, it reads saved data from external serial EEPROM and performs configuration. If external serial ROM do not exist, it reads data from internal MIO registers to perform the configuration.

#### 7.1 Serial EEPROM Information Table

When the Auto Load Tag of the external serial EEPROM have hexadecimal 55 (55h), SB16C1154PCIe start to load configuration data from serial ROM. SB16C1154PCIe can recognize whether external serial EEPROM exist or not using the AUTO Load Tag. Even though the external serial EEPROM is attached, if the value of AUTO Load Tag is not 55h, SB16C1154PCIe think there is no external serial EEPROM on I<sup>2</sup>C bus.

When the Auto Load Tag value is not 55h or there is no serial ROM, SB16C1154PCle didn't load any data from serial ROM. But SB16C1154PCle load the configuration data from MIO Register instead of external serial EEPROM.

| Address | Description             |

|---------|-------------------------|

| 00h     | Auto Load TAG (55h)     |

| 01h     | Vendor ID Low Byte      |

| 02h     | Vendor ID High Byte     |

| 03h     | Device ID Low Byte      |

| 04h     | Device ID High Byte     |

| 05h     | Revision ID             |

| 06h     | Sub Vendor ID Low Byte  |

| 07h     | Sub Vendor ID High Byte |

| 08h     | Sub System ID Low Byte  |

| 09h     | Sub System ID High Byte |

| 10h ~   | Reserved                |

Table 7–1:

Serial EEPROM Information Table

April 2014 REV 1.0 Preliminary

**Vendor ID:** It represents manufacturer of device. It is a unique ID given by PCI SIG. If you do not own Vendor ID, you can use 14A1h given to SystemBase by PCI SIG with permission.

**Device ID:** It is a unique ID of each device and is assigned at manufacturer's discretion. **Revision ID:** It is a value representing device revision.

**Sub Vendor ID:** It shows information about Subsystem manufacturer. Generally, Vendor ID or Device ID is information about Controller chip and Sub Vendor ID or Sub System ID is information about manufacturer who made the product with the chip.

Sub System ID: You can think of it as a Subsystem manufacturer's own Device ID.

#### 8. PCIe Configuration Space

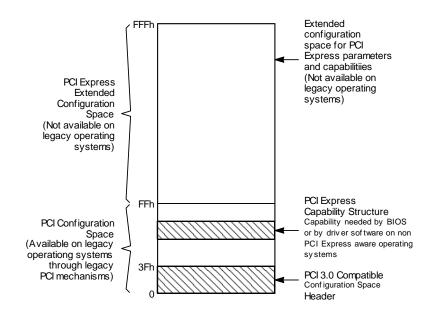

PCI Express Configuration offers two types of Configuration Space access method.

- PCI Compatible Configuration method

- PCI Express Enhanced Configuration method

PCI Compatible Configuration method is compatible with PCI version 2.3 and higher and supports 100% Binary Compatibility to software for Operating System agreed Bus list and organization.

Enhanced Configuration method offers increased Configuration Space to optimize access method. PCI Express Enhanced Configuration method uses Flat Memory-Mapped Address Space to access Configuration Register. In this case, memory address determines configuration register for access and memory data returns contents of the register that was addressed.

PCI Express provides 4096 bytes for Configuration Space per device function. This is a great increase compared to PCI Local Bus Specification, Revision 2.3 which provided 256 bytes only.

From 0 byte up to 256 bytes is called PCI Compatible Configuration Space and from 256 bytes to 4096 bytes is called Enhanced Configuration Space. This part has areas for configuring unique characteristics of PCI Express.

Figure 8–1: PCI Express Configuration Space block Diagram

#### 8.1 Configuration Registers

#### 8.1.1 Configuration Register Types

Field of Configuration Register is allocated to one of following described attributes

| Table 8–1: | Configuration | Register Types |

|------------|---------------|----------------|

|------------|---------------|----------------|

| Register<br>Attribute | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HwInit                | <b>Hardware Initialized:</b> Register bits are initialized through firmware or hardware methods like pin strapping or serial EEPROM. (System firmware hardware initialization is only permitted to system integrated devices). Bits became read-only after they are initialized and Reset with Fundamental Reset is only possible. (Write is possible only by firmware)                                   |

| RO                    | <b>Read Only:</b> Register bits are read-only and cannot be changed by software. Register bits are initialized by hardware methods like pin strapping or serial EEPROM.                                                                                                                                                                                                                                   |

| RW                    | <b>Read-Write register:</b> Register bits are readable/writeable and can either be set to a desired state or be cleared by software.                                                                                                                                                                                                                                                                      |

| RW1C                  | <b>Read-Only Status, Write-1-to-Clear Status register:</b> Register bits display status when read. The set bit indicating a status event can be cleared by writing a 1. Writing 0b to RW1C bit will not have any effect.                                                                                                                                                                                  |

| ROS                   | <b>Sticky-Read-Only register:</b> Register bits are read-only and cannot be changed by software. Registers cannot be initialized or modified by hot reset. Devices using Aux Power should preserve values of these sticky bits when using it. In these cases, the values cannot be initialized or modified by hot reset, warm reset or cold reset.                                                        |

| RWS                   | <b>Sticky-Read-Write register:</b> Register bits are readable/writeable and can either be set to a desired state or be cleared by software. Bits cannot be initialized or modified by hot reset. Devices using Aux Power should preserve values of these sticky bits when using it. These values cannot be initialized or modified by hot reset, warm reset or cold reset.                                |

| RW1CS                 | <b>Sticky-Read-Only Status, Write-1-to-Clear Status register:</b> Register bits display status when read. The set bit indicating a status event can be cleared by writing a 1. Writing 0b to RW1C bit will not have any effect. Devices using Aux Power should preserve values of these sticky bits when using it. These values cannot be initialized or modified by hot reset, warm reset or cold reset. |

| RsvdP                 | <b>Reserved and Preserved:</b> Secured for later RW implementation. Software needs to store values read in order to write on bits.                                                                                                                                                                                                                                                                        |

| RsvdZ                 | <b>Reserved and Zero:</b> Secured space for later RW1C implementation afterwards. Software uses 0b to write on bits.                                                                                                                                                                                                                                                                                      |

#### 8.1.2 Configuration Space Map of SB16C1154PCle

|        | Bit[31:24]            | Bit[23:16]             | Bit[15:8]                  | Bit[7:0]              |  |  |

|--------|-----------------------|------------------------|----------------------------|-----------------------|--|--|

| Reg000 | Dev                   | ice ID                 | Vendor ID                  |                       |  |  |

| Reg004 | Status                | Register               | Comma                      | Command Register      |  |  |

| Reg008 |                       | Class Code             |                            | Revision              |  |  |

| Reg00C | BIST                  | Header Type            | Latency Timer              | Cache Line Size       |  |  |

| Reg010 |                       | BAF                    | R0 (UART)                  |                       |  |  |

| Reg014 |                       | BAR1 (OP               | TION REGISTER)             |                       |  |  |

| Reg018 |                       | BAR2                   | 2 (Reserved)               |                       |  |  |

| Reg01C |                       | BAR                    | 3 (Reserved)               |                       |  |  |

| Reg020 |                       | BAR4                   | l (Reserved)               |                       |  |  |

| Reg024 |                       | BAR5                   | 5 (Reserved)               |                       |  |  |

| Reg028 |                       | CardBu                 | us CIS Pointer             |                       |  |  |

| Reg02C | Subsy                 | stem ID                | Subsyst                    | em Vendor ID          |  |  |

| Reg030 |                       | Expans                 | ion ROM BAR                |                       |  |  |

| Reg034 |                       | Reserved               |                            | Cap. Pointer          |  |  |

| Reg038 |                       | R                      | leserved                   |                       |  |  |

| Reg03C | Max_Lat               | Min_Gnt                | Interrupt Pin              | Interrupt Line        |  |  |

|        | (You can acc          | ess the PCI Standard C | apability Structures using | g capability pointer) |  |  |

|        |                       | Power Mana             | agement Capability         |                       |  |  |

| +0x4   |                       | Power Manage           | ment Control & Status      |                       |  |  |

|        |                       |                        |                            |                       |  |  |

|        |                       | MSI Capability         |                            |                       |  |  |

| +0x4   |                       | MSI Low                | / 32-bit Address           |                       |  |  |

| +0x8   |                       | MSI High               | n 32-bit Address           |                       |  |  |

| +0xC   | Res                   | erved                  | M                          | SI Data               |  |  |

| +0x10  |                       | Mask Bits Register     |                            |                       |  |  |

| +0x14  | Pending Bits Register |                        |                            |                       |  |  |

|        |                       |                        |                            |                       |  |  |

|        | PCIe Capab            | ilities Register       | Next Cap Pointer           | PCle Cap. ID          |  |  |

| +0x4   |                       | PCIe Device            | Capabilities Register      |                       |  |  |

| +0x8   | Device                | e Status               | Device Control             |                       |  |  |

| +0xC   |                       | PCIe Link C            | apabilities Register       |                       |  |  |

| +0x10  | Link                  | Status                 | Lin                        | k Control             |  |  |

| +0x24  |                       | Device                 | Capabilities 2             |                       |  |  |

| +0x28  | Device                | Status 2               | Device Control 2           |                       |  |  |

| +0x2C  |                       | Link C                 | Capabilities 2             |                       |  |  |

| +0x30  | Link S                | Status 2               | Link                       | Control 2             |  |  |

#### Table 8–2: Configuration Space Map

## SB16C1154PCle

PCIe End Point Controller with Quad-UART

April 2014 REV 1.0 Preliminary

|      | VPD Capability ID                     |

|------|---------------------------------------|

| +0x0 | VPD Control and Capabilities Register |

| +0x4 | VPD Data Register                     |

Configuration Space of SB16C1154PCIe can be divided into 4 following functions.

- PCI Compatible Configuration Registers

- Power Management Registers

- MSI(Message Signaled Interrupt) Registers

- PCI Express Specific Configuration Registers

PCI Compatible Configuration Registers are from Reg000 to Reg03C and these parts are compatible with existing PCI Configuration Registers. Power Management Registers, MSI Registers and PCI Express Specific Configuration Registers could be accessible by capability pointer from PCI configuration Registers.

#### 8.2 PCI Compatible Configuration Registers of SB16C1154PCIe

|        | Bit[31:24]            | Bit[23:16]          | Bit[15:8]      | Bit[7:0]        |  |  |

|--------|-----------------------|---------------------|----------------|-----------------|--|--|

| Reg000 | Devi                  | ce ID               | Vendor ID      |                 |  |  |

| Reg004 | Status I              | Register            | Comm           | and Register    |  |  |

| Reg008 |                       | Class Code          |                | Revision        |  |  |

| Reg00C | BIST                  | Header Type         | Latency Timer  | Cache Line Size |  |  |

| Reg010 |                       | BAF                 | R0 (UART)      |                 |  |  |

| Reg014 |                       | BAR1 (OPT           | FION REGISTER) |                 |  |  |

| Reg018 |                       | BAR2                | (Reserved)     |                 |  |  |

| Reg01C |                       | BAR3 (Reserved)     |                |                 |  |  |

| Reg020 |                       | BAR4 (Reserved)     |                |                 |  |  |

| Reg024 |                       | BAR5 (Reserved)     |                |                 |  |  |

| Reg028 |                       | CardBus CIS Pointer |                |                 |  |  |

| Reg02C | Subsys                | stem ID             | Subsys         | tem Vendor ID   |  |  |

| Reg030 |                       | Expansion ROM BAR   |                |                 |  |  |

| Reg034 | Reserved Cap. Pointer |                     |                |                 |  |  |

| Reg038 |                       | Reserved            |                |                 |  |  |

| Reg03C | Max_Lat               | Min_Gnt             | Interrupt Pin  | Interrupt Line  |  |  |

Table 8–3:

Compatible Configuration Registers

SB16C1154PCIe uses Configuration Register of Header Type0 which is used as Endpoint.

Following is a detailed description of PCI Compatible Configuration Register.

#### 8.2.1 Vendor ID

A 16-bit register which represents the manufacturer of the device. It is a unique ID given by PCI SIG after membership registration. If you do not own a

April 2014 REV 1.0 Preliminary

Vendor ID, it is fine to use 14A1h given to SystemBase by PCI SIG. [HwInit]

#### 8.2.2 Device ID

A 16-bit unique ID of each device given by the Function Manufacturer which can be assigned by the manufacturer freely.

It is related to software driver installation/recognition. [HwInit]

#### 8.2.3 Command Register

#### Table 8–4: Command Register

| Bit    | Туре | Description                                                                                     |

|--------|------|-------------------------------------------------------------------------------------------------|

| 15:11  | RO   | Reserved:                                                                                       |

| 10     | RW   | INTx Assertion Disable: This bit controls PCI Express function's INTx interrupt message         |

|        |      | creation ability. When it is 0b, function can create INTx interrupt message. When it is 1b,     |

|        |      | function cannot create INTx interrupt message. Although this bit is set after the Assert_INTx   |

|        |      | emulation interrupt message is transmitted, Deassert_INTx interrupt message must be sent        |

|        |      | to finish the Assert_INTx that was sent earlier. Default value of this bit is 0b.               |

| 9      | RO   | Fast Back-to-Back Enable: It is not applied to PCI Express and hardwired to 0b.                 |

| 8      | RW   | SERR Enable: If this bit is set and the function detects a non-fatal error and a fatal error,   |

|        |      | error reporting is executed to Root Complex. You can set the kind of errors to report to Device |

|        |      | Control Register. Default value is 0b.                                                          |

| 7      | RO   | IDSEL Stepping/Wait Cycle Control: It is not applied to PCI Express and hardwired to 0b.        |

| 6      | RW   | Parity Error Response: A Root Complex Integrated Endpoint that is not associated with a         |

|        |      | Root Complex Event Collector is permitted to hardwire this bit to 0b. Default value is 0b.      |

| 5      | RO   | VGA Palette Snoop: It is not applied to PCI Express and hardwired to 0b.                        |

| 4<br>3 | RO   | Memory Write and Invalidate: It is not applied to PCI Express and hardwired to 0b.              |

| 3      | RO   | Special Cycle Enable: It is not applied to PCI Express and hardwired to 0b.                     |

| 2      | RW   | Bus Master Enable: When it is 0b, it cannot operate as master. When it is 1b, it can start      |

|        |      | transaction as master. Enables the device to operate as master but is hardwired to 0b since     |

|        |      | this device does not create transaction.                                                        |

| 1      | RW   | Memory Space Enable: When it is 0b, Memory Decoder is disabled and Memory                       |

|        |      | Transactions arriving to this device are responded with Completion of Unsupported Request       |

|        |      | state.                                                                                          |

|        |      | When it is 1b, Memory Decoder is enabled and memory transactions arriving to this device        |

|        |      | are accepted and handled.                                                                       |

| 0      | RW   | IO Space Enable: When it is 0b, IO decoder is disabled and IO transactions arriving to this     |

|        |      | device are responded with Completion of Unsupported Request state. When it is 1b, IO            |

|        |      | decoder is enabled and IO transactions arriving to this device are accepted and handled.        |

April 2014 REV 1.0 Preliminary

#### 8.2.4 Status Register

Table 8–5: Status Register

| Bit  | Туре | Description                                                                                     |

|------|------|-------------------------------------------------------------------------------------------------|

| 15   | RW1C | Detected Parity Error: This bit is set when function receives poisoned TLP. It is not related   |

|      |      | with Command Register's Parity Error Enable bit status. Default value of this bit is 0b.        |

| 14   | RW1C | Signaled System Error: This bit is set when Command Register's SERR Enable bit is set           |

|      |      | and function transmits ERR_FATAL or ERR_NONFATAL message. Default value of this bit is          |

|      |      | 0b.                                                                                             |

| 13   | RW1C | Received Master Abort: This bit is set when requester receives Completion of Unsupported        |

|      |      | Request Completion Status. Default value of this bit is 0b.                                     |

| 12   | RW1C | Received Target Abort: This bit is set when requester receives Completion of Completer          |

|      |      | Abort Completion Status. Default value of this bit is 0b.                                       |

| 11   | RW1C | Signaled Target Abort: This bit is set when a request is completed by Completer Abort           |

|      |      | Completion Status. Default value of this bit is 0b.                                             |

| 10:9 | RO   | DEVSEL Timing.                                                                                  |

|      |      | It is not applied to PCI Express and hardwired to 0b.                                           |

| 8    | RW1C | Master Data Parity Error: It is set when Parity Error Enable bit of Command Register is set     |

|      |      | and following two cases occur.                                                                  |

|      |      | - When requester receives Poisoned Completion.                                                  |

|      |      | - When requester's write request is Poisoned.                                                   |

|      |      | If Parity Error Enable bit is cleared, this bit is not set.                                     |

| 7    | RO   | Fast Back-to-Back Capable: It is not applied to PCI Express and hardwired to 0b.                |

| 6    | RO   | Reserved.                                                                                       |

| 5    | RO   | 66MHz-Capable: It is not applied to PCI Express and hardwired to 0b.                            |

| 4    | RO   | Capabilities List: Shows that there is 1 or more extended capability register set.              |

|      |      | This bit should be set to 1b since SB16C1154PCIe possesses Extended Capability register         |

|      |      | range.                                                                                          |

| 3    | RO   | INTx Status: Indicates that the function has an interrupt request that has not been processed   |

|      |      | yet. (Function is waiting to be serviced after sending an interrupt message. In other words, it |

|      |      | is 1b when Assert_INTx is sent and Deassert_INTx is not.) This bit is only related to INTx      |

|      |      | message and has no meaning when using Message Signaled Interrupt.                               |

| 2:0  | RO   | Reserved.                                                                                       |

#### 8.2.5 Revision

This register shows device revision. Manufacturer can assign it freely. It is also related to software device driver installation.

#### 8.2.6 Class Code

This register contains descriptions on functions the device implements. It is divided as Base Class, Sub Class and Programming Interface in bytes. It must be set to the values provided by PCI Express Bus Specification.

SB16C1154PCIe gets 07\_00\_02h since it is a serial communication card adaptor.

April 2014 REV 1.0 Preliminary

Base Class Code is 07h(communication controller), Sub Class Code is 00h(serial controller) and Programming Interface is 02h(16C550 compatible).

#### 8.2.7 Cache Line Size

This register assigns size of system's Cache Line. It is implemented as [RW] for compatibility with existing PCI and does not affect functioning of PCI Express.

#### 8.2.8 Latency Timer

This register assigns latency clock related to bus master which does burst access. It is not applied to PCI Express and is hardwired to 0b.

#### 8.2.9 Header Type

Configuration Space Header type and [ RO]

Bit[7] : Shows whether device is Multi Function or Single Function. This product has default value 0b since it only supports Single Function.

Bit[6:0] : Assign header type after 10h. 00h is target device, 01h is PCI-to-PCI Bridge and 02h is CardBus bridge. This product has default value 00 since it is a target device.

#### 8.2.10 BIST(Built-In Self Test)

#### Table 8–5: BIST

| Bit | Туре | Description                                                                                       |

|-----|------|---------------------------------------------------------------------------------------------------|

| 7   | RO   | BIST Capable: Displays 1b if BIST is implemented and displays 0b if it is not implemented.        |

| 6   | RO   | Start BIST: Function's BIST starts when this bit is set to 1b and after BIST finishes, the bit is |

|     |      | cleared to 0b.                                                                                    |

| 5:4 | RO   | Reserved:                                                                                         |

| 3:0 | -    | Completion Code: Display 0b for successful completion and other values for Function-              |

|     |      | specific errors.                                                                                  |

#### 8.2.11 Base Address Registers

These are spaces for assigning Base address for accessing I/O device or memory on PCI Express Local Bus. There are 2 spaces from Base Address Register 0 to 5 but spaces from Base Address Register 2 to 5 are set as unused reserved area. In SB16C1154PCIe, Base Address Register 0 is used for UART Space and Base Address Register 1 is used for Option Registers Space. Both of these Base Address Register spaces are used as space for I/O. When Base Address Register Bit[0] is 0b, the space is used as Memory space and when 1b, it is used as I/O space. You can select the memory space or I/O space of BAR0 and BAR1 using 'BARSEL' input pin.

#### 8.2.11.1 Base Address Register0

SB16C1154PCIe operates Serial 4-port Mode. The size of memory or I/O address space is from 00h to 7Fh. (1 channel has 00h ~ 1Fh space.)

See '9. SB16C1154PCIe Register Description' for more details.

April 2014 REV 1.0 Preliminary

#### 8.2.11.2 Base Address register1

Aside from UART area, SB16C1154PCIe contains Option Registers area which controls overall operations of the SB16C1154PCIe. SB16C1154PCIe sets this area with Base Address Register1(BAR1. Memory or I/O Address space size of the Option I/O Register is from 00 to 1Fh.

See '9. SB16C1154PCIe Register Description' for more details.

#### 8.3 Power Management Registers of SB16C1154PCle

Sometimes controlling over power is needed on PCI Express Bus applied systems. Especially in cases when system uses independent power source like mobile system or when PCI device occupies a lot of power but it is not used, the system must limit power supply to PCI device for making a power efficient system. For this reason, PCI specification provides Power Management Interface Specification making Power Management more convenient. This Power Management Capability Structures Registers could be accessed by capability pointer through linked list of capability register sets. SB16C1154PCIe supports 'PCI Power Management Interface Specification Space Header is shown below. See 'PCI Power Management Interface Spec. Rev 1.2' for more details.

#### Table 8–7: Power Management Register Block

+0x4

|   | Power manageme | nt Capabilities (PMC) | Next Item Ptr                   | Capability ID (0x01) |  |

|---|----------------|-----------------------|---------------------------------|----------------------|--|

|   | Data           | PMCSR_BSE Bridge      | Power Ma                        | Power Management     |  |

| 4 | Dala           | Support Extensions    | Control/Status Register (PMCSR) |                      |  |

#### 8.3.1 Capability ID (offset: 0x0)

Capability ID regarding Power Management Interface and the value is 01h. (default)

#### 8.3.2 Pointer to Next Capability (offset: 0x01)

A pointer storing address of register which has information about next Capability. You can find next Capability from other different Capability List by following this address. SB16C1154PCIe supports MSI Capability List and has the pointer to it which has the value 48h. See '*PCI Spec. Rev 3.0*' and '*PCI Express Base Spec. Rev 1.1*' for more details.

April 2014 REV 1.0 Preliminary

| Table 8–8: | Power Management Capabilities |                                                                                                  |  |  |

|------------|-------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| Bit        | Туре                          | Description                                                                                      |  |  |

| 15:11      | RO                            | PME_Support: Shows condition of PME Message transmission. SB16C1154PCIe can                      |  |  |

|            |                               | receive PME Message in D3 <sub>hot</sub> and D3 <sub>cold</sub> states and has value of 1_1001b. |  |  |

|            |                               | Bit11: When set, PME Messages can be generated from D0                                           |  |  |

|            |                               | Bit12: When set, PME Messages can be generated from D1                                           |  |  |

|            |                               | Bit13: When set, PME Messages can be generated from D2                                           |  |  |

|            |                               | Bit14: When set, PME Messages can be generated from D3hot                                        |  |  |

|            |                               | Bit15: When set, PME Messages can be generated from D3cold                                       |  |  |

| 10         | RO                            | D2_Support: Tells whether function supports D2 Power Management State. This device               |  |  |

|            |                               | does not support D2 state and has value of 0b.                                                   |  |  |

| 9          | RO                            | D1_Support: Tells whether function supports D1 Power Management State. This device               |  |  |

|            |                               | does not support D1 state and has value of 0b.                                                   |  |  |

| 8:6        | RO                            | Aux Current: Report VIO_AUX auxiliary current requirements for this function.                    |  |  |

|            |                               | Function of this device is configured to require 375mA which is maximum support                  |  |  |

|            |                               | capacity of an electric current supply and has value of 111b.                                    |  |  |

| 5          | RO                            | Device-Specific Initialization (DSI): Shows need of DSI after transition from D3 to D0           |  |  |

|            |                               | uninitialized state. It should be set to 1b since initial value configuration for UART's         |  |  |

|            |                               | communication is needed here.                                                                    |  |  |

| 4          | RO                            | Reserved:                                                                                        |  |  |

| 3          | RO                            | PME Clock: It is not applied to PCI Express and hardwired to 0b.                                 |  |  |

| 2:0        | RO                            | Version: Compatible with PCI PM Specification V1.2 and has value of "011".                       |  |  |

#### 8.3.3 Power Management Capabilities (offset: 0x02)

#### 8.3.4 Power Management Control/Status Register (offset: 0x04)

This 16bit Register manages PCIe Function's Power Management state and it is also used to enable and monitor PME.

April 2014 REV 1.0 Preliminary

| Bit   | Туре | Description                                                                                      |

|-------|------|--------------------------------------------------------------------------------------------------|

| 15    | RW1C | PME_Status: PME_Status is set to 1b after receiving PME Message and when PM S/W                  |

|       |      | writes 1b, it is cleared.                                                                        |

| 14:13 | RO   | Data Scale: This device did not implement Data Scale and it is 00b.                              |

| 12:9  | RO   | Data Select: This device did not implement Data Select and it is 0000b                           |

| 8     | RWS  | PME_EN: If PME_En equals 1b, receiving PME Message becomes possible. If PME_En                   |

|       |      | equals 0b, PME Message cannot be received. If receiving PME Message in D3 <sub>cold</sub> state  |

|       |      | becomes possible, this value is unclear at OS booting time and it is Read/Written by PM          |

|       |      | S/W. (RWS) If receiving PME Message in D3 <sub>cold</sub> state is not possible, this bit is 0b. |

| 7:4   | RO   | Reserved: Always zero.                                                                           |

| 3     | RO   | No_Soft_Reset: Device does not execute internal reset when changing from D3 <sub>hot</sub> to    |

|       |      | D0 through software control of PowerState bits. It's because full Re-Initialization is not       |

|       |      | needed for device to return to D0. Its value is 0b.                                              |

| 2:0   | RO   | PowerState: PM S/W can decide Power Management state by configuring this section.                |

|       |      | PowerState = 00b means D0 state                                                                  |

|       |      | PowerState = 01b means D1 state                                                                  |

|       |      | PowerState = 10b means D2 state                                                                  |

|       |      | PowerState = 11b means D3 state                                                                  |

#### Table 8–9: Power Management Control/Status Register

#### 8.3.5 PMCSR PCI-to-PCI Bridge Support Extensions (offset: 0x06)

PMCSR\_BSE supports PCI bridge specific functions and is essential to all PCI-to-PCI Bridge. SB16C1154PCIe does not support it since it is an Endpoint. (00h)

#### 8.3.6 Power Management Data Register (offset: 0x07)

Data register is an option and is a 8bit read only register. It shows power consumed and heat dissipation. SB16C1154PCIe does not support it and when read, 00h is returned.

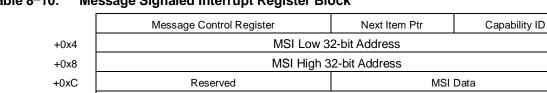

#### 8.4 Message Signaled Interrupt Registers of SB16C1154PCIe

Existing PCI Bus used control signals of Side Band for various kinds of required controls. Interrupt was also controlled with INTA, INTB, INTC, INTD signals of Side Band signal. However, all Side Band signals disappeared from PCI Express since it uses Serial Bus and the use of In Band Bus signals became necessary. Consequently, all interrupts are handled in Message Type.

Two ways of interrupt transmission of PCI Express Bus are shown below.

- Native PCI Express Interrupt Delivery – MSI

- Legacy PCI Interrupt Delivery – INTx Message

We provide MSI Capability to support Message Signaled Interrupt which is used by Native PCI Express Device. This MSI(Message Signaled Interrupt) Capability Structures Registers could be accessed by capability pointer through linked list of capability register sets. And this Capability Block is compatible with existing MSI of PCI 3.0 and provides the same functions. Following is a Map of MSI Capability List.

#### Table 8–10: Message Signaled Interrupt Register Block

#### 8.4.1 Capability ID (offset: 0x0)

Capability ID for MSI register and default value is 05h.

Mask Bits Register

Pending Bits Register

#### 8.4.2 Pointer to Next Capability (offset: 0x01)

Pointer storing address of register which has information about next Capability. You can find next Capability from other different Capability List by following this address. SB16C1154PCIe supports PCI Express Capability List and has the pointer to it that has the value 60h. See PCI Express Base Spec. for more details.

#### 8.4.3 Message Control Register (offset: 0x02)

MSI Low 32-bit Address & MSI High 32-bit Address